## VEER SURENDRA SAI UNIVERSITY OF TECHNOLOGY (VSSUT), ODISHA Odd Mid Semester Examination for session 2024-25

COURSE NAME:

SEMESTER: 3rd

**BRANCH NAME: EEE**

SUBJECT NAME: Analog Electronics Circuit

**FULL MARKS: 30**

TIME: 90 Minutes

Answer All Questions.

The figures in the right hand margin indicate Marks. Symbols carry usual meaning.

Q1. Answer all Questions.

$\{2\times3\}$

What are the biasing conditions for different operating regions of BJT?

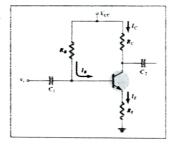

(b) Explain Emitter follower circuit.

Write output current equation for Depletion and Enhancement type MOSFET.

<u>9</u>2. علا

What is biasing? Explain Emitter-biasing circuit with neat diagram.

[8]

For emitter bias network, determine I<sub>C</sub>, V<sub>CE</sub>, V<sub>C</sub>, V<sub>E</sub>

Given  $R_B = 430 \text{ k}\Omega$ ,  $V_{cc} = 20 \text{ v}$

$R_C = 2 k\Omega$

$R_E = 1 k\Omega$

$\beta = 50$

OR

- Explain fixed bias circuit with neat diagram. Compare the stability criteria with Emitter bias.

- b) What is quiescent point? What is the preferred location of the operating point for faithful amplification and why?

**[8]**

Q3.

Explain the h-parameter model and find Av Ai Zi Zo for common emitter fixed bias configuration.

OR

Explain the  $r_c$ -model and compute the parameters for common emitter fixed bias configuration.

94. a)

Sketch the transfer characteristics of an n-channel depletion type MOSFET with  $I_{DSS} = 10 \text{mA}$  and  $V_n = -4V$ .

b) Determine the following for the circuit. Given  $I_{DSS} = 10 \text{ mA}$ ,  $V_{P} = -8 \text{ V}$

OR

Compare fixed bias and emitter bias for n-channel JFET using DC analysis.