# Automatización del proceso de diseño para un Nanochip

Juan Pablo Mora Argueta, PROFESOR: Jonathan de los Santos Departamento de Ingeniería Electrónica y Biomédica

mor15799@uvg.edu.gt, jadelossantos@uvg.edu.gt

# **RESUMEN**

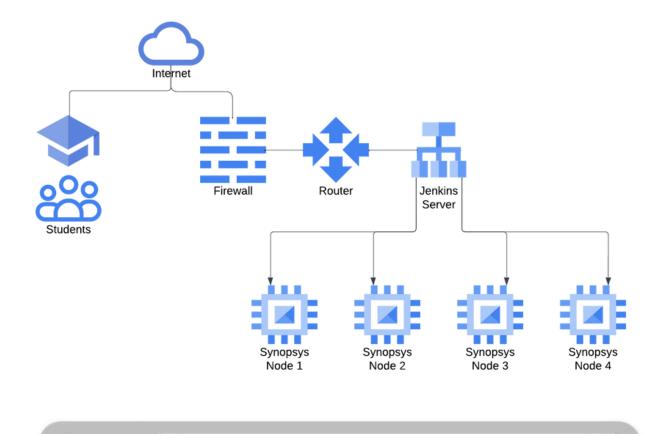

Este trabajo facilita el acceso de los estudiantes a herramientas de diseño electrónico automatizado (EDA), superando las dificultades de instalación en Linux. Se creó un pipeline con interfaz web que permite cargar archivos Verilog y procesarlos en un entorno controlado, accediendo a librerías de TSMC protegidas por copyright sin interacción directa. Los resultados:

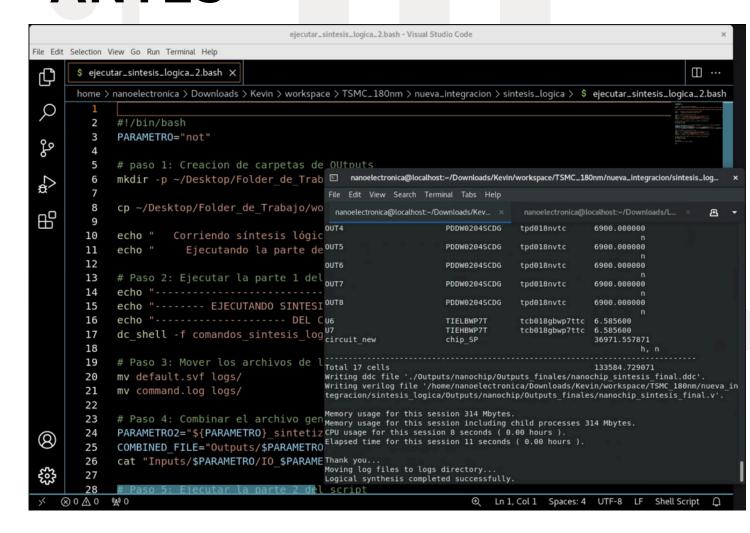

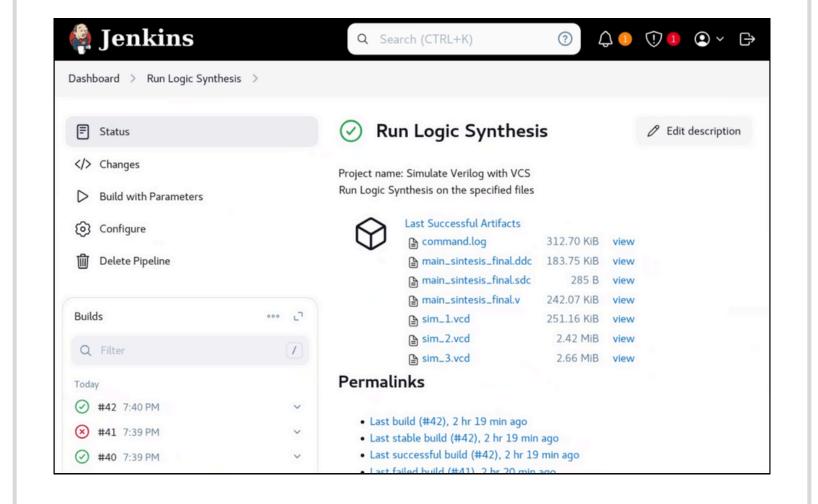

- Automatización eficiente: Integración de síntesis lógica y física, simulando Verilog vía Jenkins.

- **Uso de contenedores**: Implementación de Apptainer para entornos portables y reproducibles, simplificando la gestión de dependencias.

- Documentación detallada: Guía completa para instalación, configuración y depuración.

- Adaptación de herramientas Synopsys: Integración de VCS, icc2\_shell e IC Validator para manejar diseños complejos.

Este proyecto reduce barreras de entrada y potencia el aprendizaje práctico de los estudiantes en EDA.

## **OBJETIVOS**

#### Objetivo General:

Simplificar el diseño de nanochips con herramientas de Synopsys mediante la automatización de procesos como contenedores, integración continua y compilación automática.

#### **Objetivos Específicos:**

- Instalar las herramientas de Synopsys en contenedores.

- Configurar su ejecución desde la línea de comando con parámetros predecibles.

- Documentar detalladamente la instalación y configuración de la plataforma elegida.

- Implementar una cadena de integración continua para automatizar la compilación de Verilog.

Configurar alertas descriptivas para notificar errores en

- Configurar alertas descriptivas para notificar errores en el proceso.

- Crear configuraciones reutilizables para futuros proyectos de diseño de chips.

## **MÉTODOS**

# **RESULTADOS**

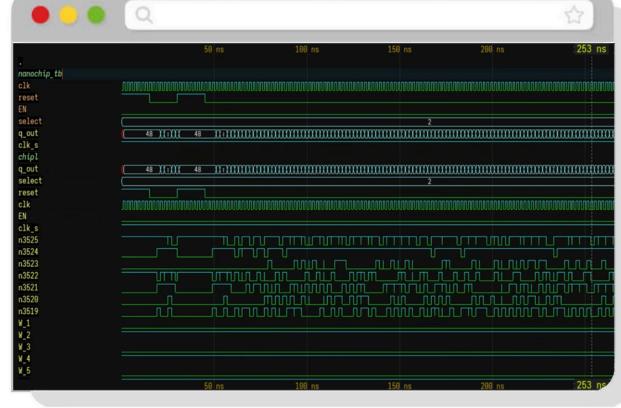

- Automatización Eficiente: Se crearon procesos automáticos que permiten simular diseños electrónicos en menos de un minuto, utilizando solo una interfaz web y un archivo de entrada.

- Entornos Portables: Se implementaron contenedores que hacen los sistemas más compatibles y fáciles de usar en diferentes computadoras, eliminando problemas de instalación.

- **Guía Práctica:** Se elaboró un manual detallado que explica cómo instalar, configurar y solucionar problemas en los procesos automatizados.

- Uso de Herramientas de Synopsys: Se integraron programas especializados que simplifican el diseño y verificación de circuitos complejos de manera confiable.

### **ANTES**

## **AHORA**

## CONCLUSIONES

- El proyecto simplificó el acceso a herramientas de diseño electrónico automatizado (EDA) al eliminar las barreras de instalación en Rocky Linux mediante pipelines automatizados y contenedores Apptainer.

- Se logró procesar archivos Verilog en menos de un minuto a través de una interfaz web, cumpliendo los objetivos de crear entornos controlados, reproducibles y compatibles.

- La documentación detallada facilitó la instalación y uso de herramientas avanzadas, sirviendo como referencia para futuros proyectos.

- Las alertas configuradas para errores mejoraron la depuración y aumentaron la confiabilidad del proceso.

- Se optimizó la eficiencia en todos los flujos de trabajo relacionado con Synopsys, reduciendo la complejidad técnica y proporcionando una solución accesible para estudiantes y proyectos futuros.

# TRABAJO FUTURO

- Uso de Artifacts en procesos posteriores.

- Estrategias de retención de Artifacts.

- Integración de un graficador web para archivos VCD.

Permitir el acceso desde internet al pipeline creado.

- Escalabilidad el sistema a través de nodos o *workers* adicionales.