# Nanochip: Generación de síntesis física y verificaciones finales con librerías de TSMC

Lourdes María Ruiz Vásquez, M.Sc. Jonathan Alberto de los Santos Chonay Departamento de Ingeniería Electrónica, Mecatrónica, Biomédica rui20275@uvg.edu.gt, jadelossantos@uvg.edu.gt

## Resumen

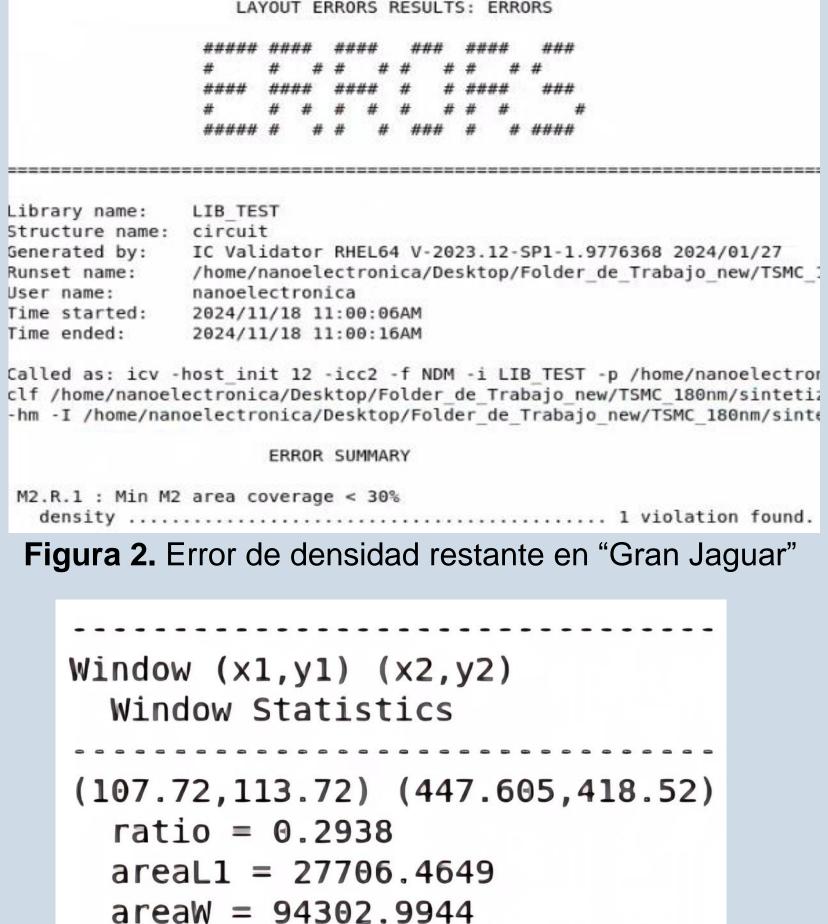

Este trabajo se centró en mejorar el flujo de síntesis basándose en avances previos y automatizando aún más el proceso. Se abordaron errores al ejecutar los scripts de síntesis e identificaron áreas de mejora como la generación de archivos Verilog y la definición de variables para valores repetidos. Tras implementar estos cambios, realizaron síntesis de múltiples circuitos, verificaciones DRC y de antena, logrando cumplir con los requisitos mínimos de fabricación en la mayoría de los casos, excepto en el circuito "Gran Jaguar", cuya densidad en la capa de Metal 2 fue de 29.3%, por debajo del mínimo requerido del 30%.

Además, se realizaron pruebas funcionales con HSPICE y WaveView para validar el diseño y se documentaron las etapas del flujo en un manual. De cara al futuro, se recomienda trabajar en un flujo de diseño más automatizado, capaz de ajustar dimensiones según características específicas y mejorar el mapeo de pines tras la extracción de parásitos.

# Objetivos

#### **Objetivo General**

Generar documentación detallada y verificaciones finales del proceso de diseño de un circuito integrado, para que sea replicable por futuras generaciones de estudiantes de la UVG.

#### Objetivos específicos

- Replicar trabajos anteriores para aprender y dominar el proceso de diseño y pruebas de funcionamiento incluyendo síntesis verificaciones físicas y extracción de parásitos.

- Realizar síntesis física y las verificaciones físicas de Antena y DRC.

- Documentar la fase de síntesis física para que pueda servir de referencia en futuros trabajos.

- Resolver errores de densidad restantes al ejecutar DRC.

- Realizar verificaciones finales de funcionamiento, posterior a la extracción de parásitos.

- Verificar el cumplimiento de los requisitos de TSMC y mantener comunicación con IMEC

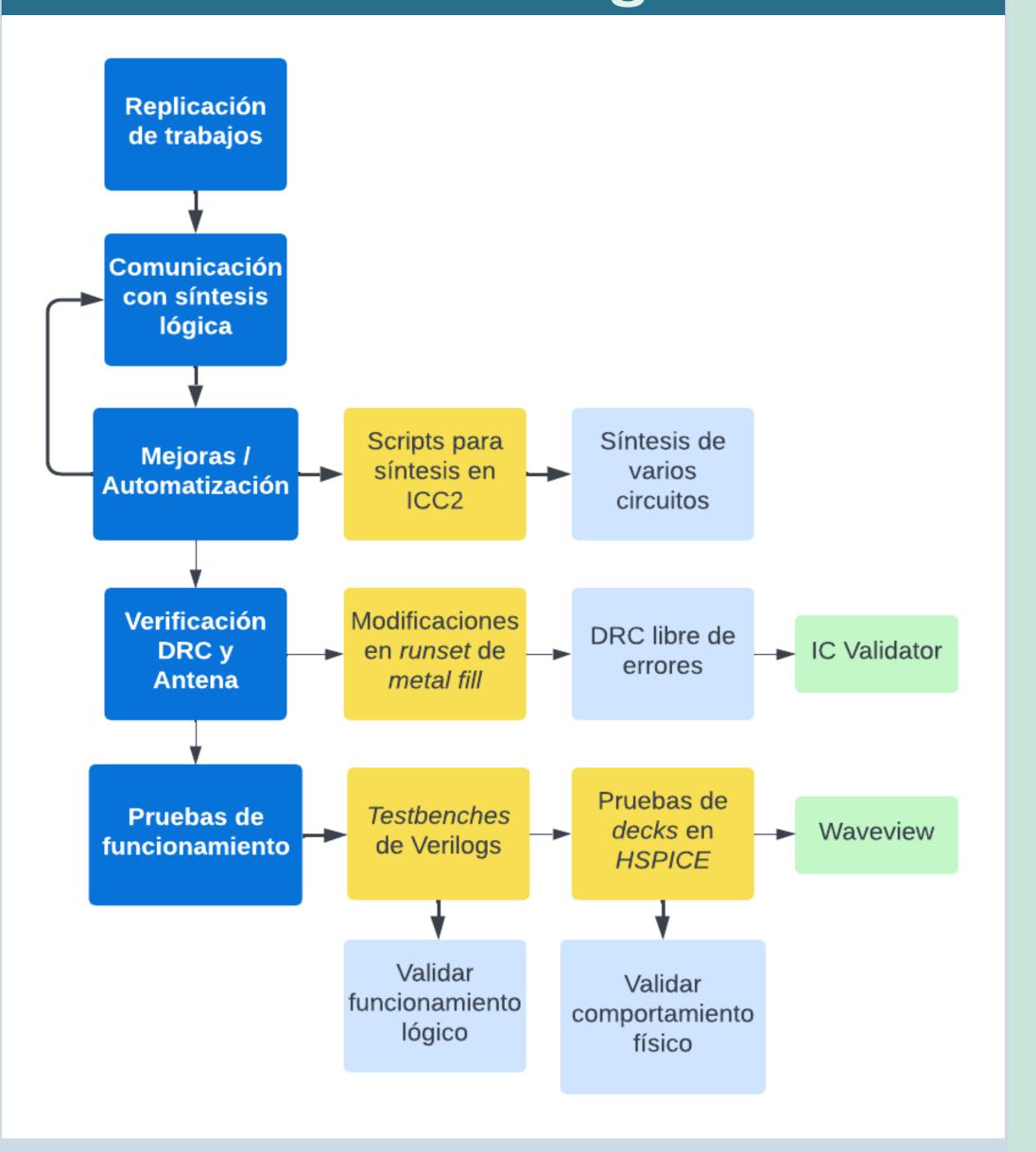

# Metodología

## Resultados

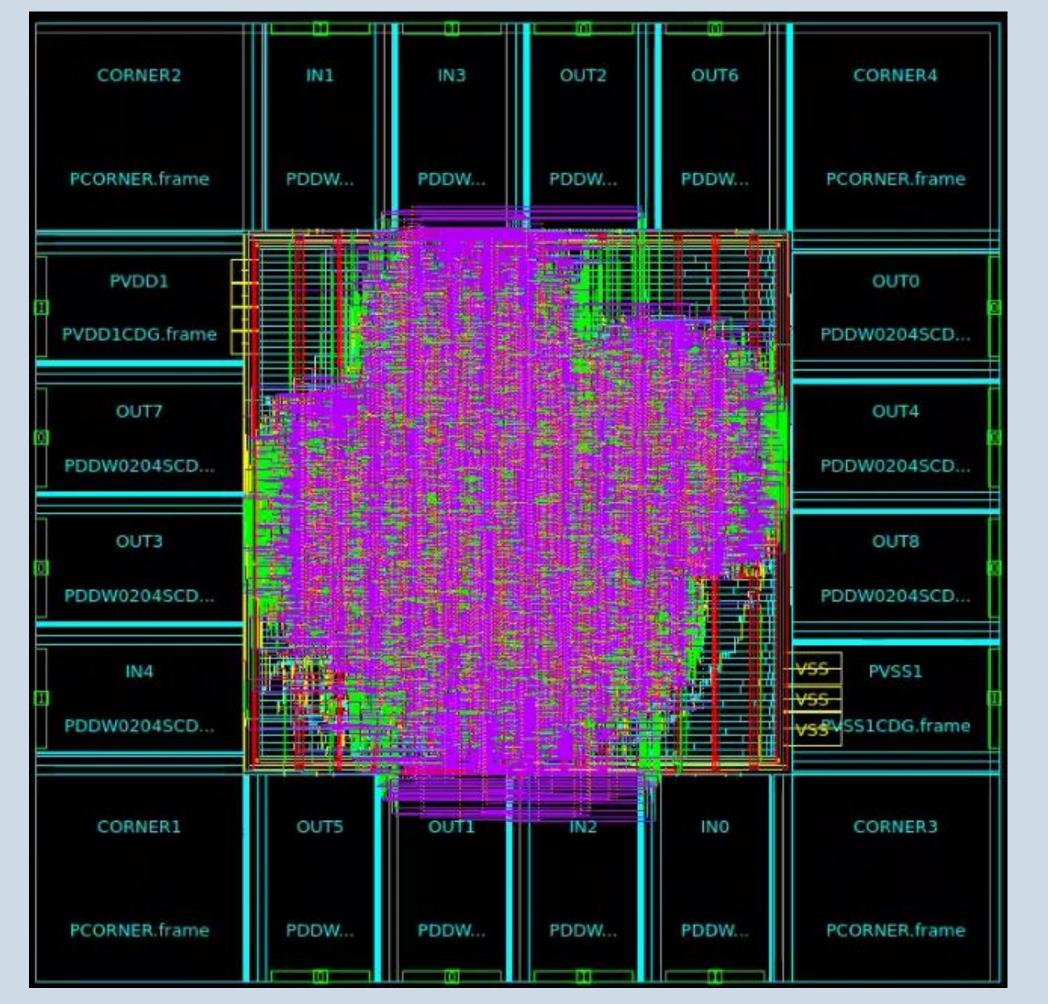

Figura 1. Layout del circuito "Gran Jaguar"

Figura 3. Porcentaje de Metal 2 en "Gran Jaguar"

## Conclusiones

- Se implementaron mejoras en el flujo de síntesis física, permitiendo la automatización de funciones como la síntesis de reloj y definición de dimensiones.

- Se realizó la síntesis física de circuitos tanto de naturaleza combinacional y secuencial.

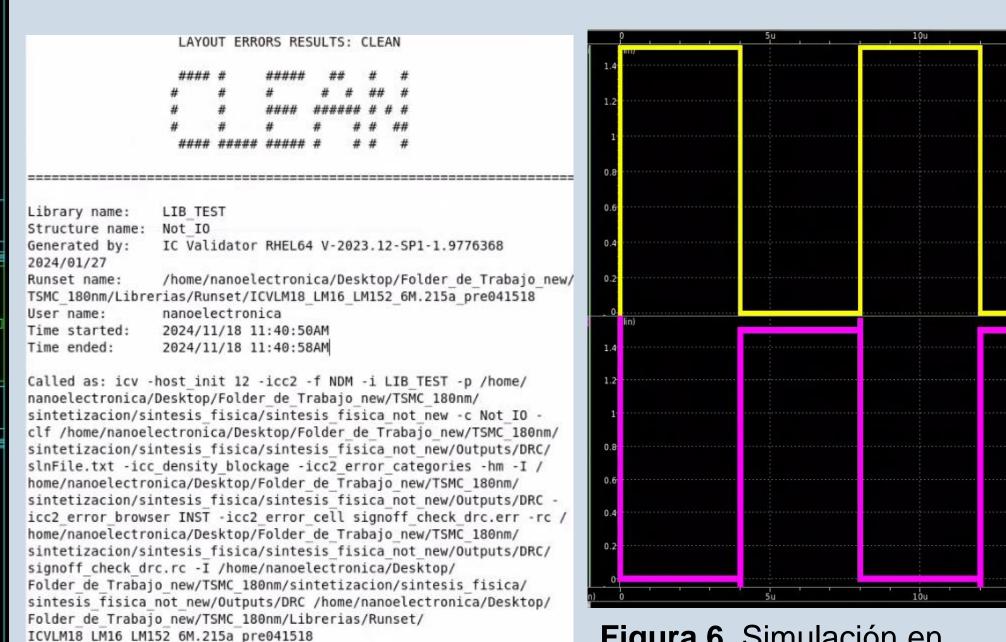

- Se llevó a cabo la verificación física DRC modificando el runset de relleno de metal, obteniendo resultados libres de errores de densidad en la mayoría de los diseños.

- Se llevó a cabo la verificación de Antena para múltiples circuitos, en los cuales se obtuvo resultados satisfactorios.

- archivo Verilog generado mantiene conexiones lógicas consistentes, pero no refleja con precisión el layout físico del circuito.

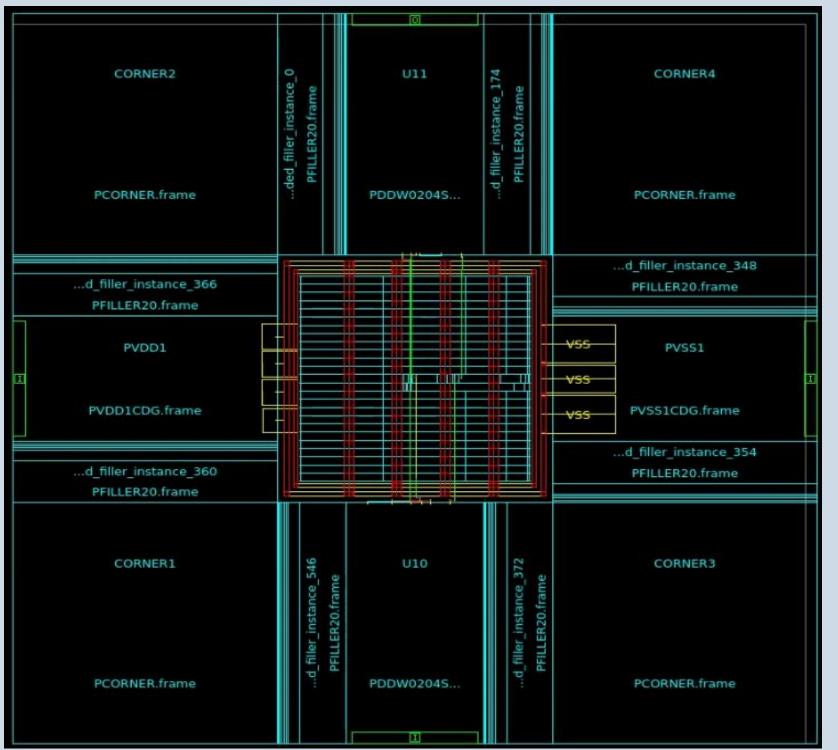

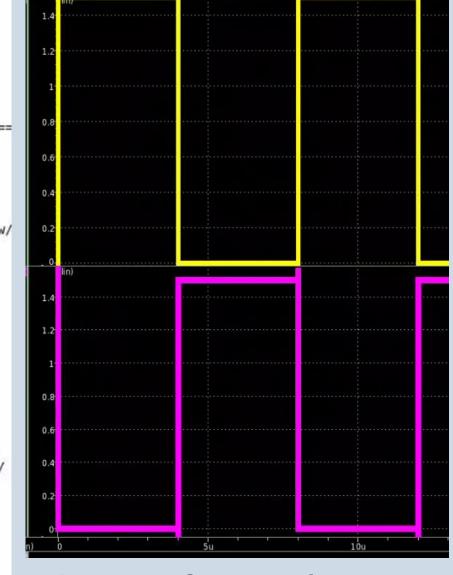

- Se realizó el mapeo de pines en el deck tras la extracción parasitaria y se validó el funcionamiento de compuertas NOT, XOR y un sumador de 4 bits.

- Se colaboró con el equipo de síntesis lógica para crear un **manual detallado y vídeos demostrativos** del flujo de diseño completo.

#### Flujo completo

Figura 4. Layout de una compuerta NOT

Figura 5. DRC para la compuerta NOT

Figura 6. Simulación en HSPICE de la compuerta NOT

## Recomendaciones

- Familiarizarse con las herramientas replicando el proceso y comenzando con diseños simples, aumentando gradualmente la complejidad.

- Comunicarse con IMEC y TSMC desde el inicio del año agilizará la obtención de documentación clave para el proyecto.

- Automatizar el proceso de mapeo de pines tras la extracción parásita mediante un algoritmo, y complementar este flujo con la creación de decks para las celdas que aún no han sido definidas.

- Investigar la optimización del diseño para crear un flujo de síntesis física autogestionado que calcule automáticamente dimensiones según características específicas.

## Video demostrativo:

## Referencias

- 1. A.Altuna, "Diseño de un Circuito Integrado con Tecnología de 180nm usando Librerías de Diseño de TSMC: Ejecución de la Síntesis Física, Verificación de Reglas de Diseño y Corrección de Errores Obtenidos.", UVG, 2021.

- 2. J. Shin, "Diseño de un Circuito Integrado con Tecnología de 180nm usando Librerías de Diseño de TSMC: Ejecución de la Síntesis Física, Verificación de Reglas de Diseño y Corrección de Errores Obtenidos.", UVG, 2021.

- 3. I.Arévalo, "Diseño de un circuito integrado con tecnología de 180 nm utilizando librerías de diseño de TSMC: Simulación en PrimeSim y análisis de errores.", UVG, 2022.

- 4. N. Prado, "Diseño de un circuito integrado con tecnología de 180 nm, utilizando las librerías de diseño de TSMC y las librerías educativas de Synopsys: corrección de errores de densidad y polisilicio, verificación DRC y antena.", UVG, 2023.

- 5. Synopsys, "IC Compiler II Implementation User Guide.", 2023.