# Nanochip: LVS, ERC y extracción de parásitos

Diana Sofía Alvarado Mota, M.Sc. Jonathan Alberto de los Santos Chonay

Departamento de Ingeniería Electrónica, Mecatrónica y Biomédica

alv20525@uvg.edu.gt, jadelossantos@uvg.edu.gt

#### **RESUMEN**

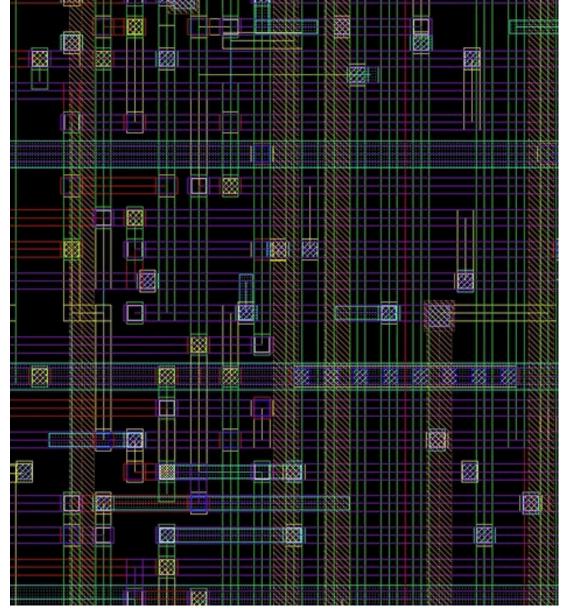

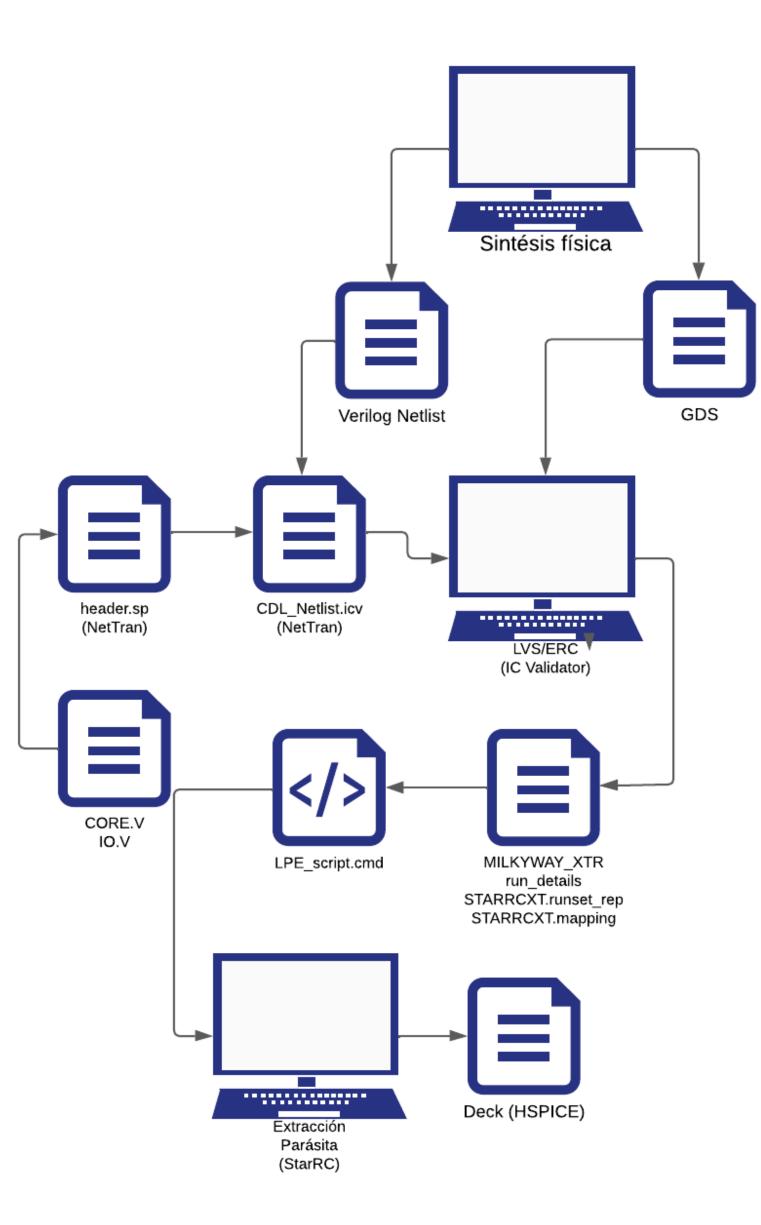

El trabajo aborda la verificación de reglas eléctricas (ERC), layout versus schematic (LVS) y extracción parásita en circuitos integrados. Utilizando herramientas como IC Compiler II, IC Validator y StarRC. Se diseñaron circuitos que van desde compuertas NOT hasta el complejo "El Gran Jaguar". Aunque se planeó trabajar con tecnología de 65 nm, por el proceso administrativo con IMEC y TSMC se optó por la tecnología de 180 nm. La extracción de resistencias parásitas se limitó a tres circuitos pequeños debido a la complejidad , y el deck para simulaciones en HSpice solo es funcional eliminando las resistencias y capacitores parásitos. Se propone automatizar el proceso mediante scripts y optimizar la creación de celdas, mejorando la eficiencia y reduciendo errores. El desarrollo de este tipo de proyectos resulta crucial en el panorama tecnológico actual, ya que los nanochips representan un avance significativo en la creación de dispositivos más pequeños, rápidos y eficientes energéticamente, con aplicaciones que abarcan desde la electrónica de consumo hasta la investigación científica avanzada.

Layout de "El Gran Jaguar"

## **OBJETIVOS**

- Realizar pruebas LVS, ERC y extracción de parásitos en un circuito de 180 nm para garantizar funcionalidad y confiabilidad.

- Replicar avances previos del proyecto de diseño de circuitos integrados

- Verificar la consistencia entre diseño esquemático y físico mediante pruebas LVS.

- Comprobar cumplimiento de normativas eléctricas con pruebas ERC.

- Extraer parásitos para obtener un deck simulable y mejorar la precisión de las simulaciones finales.

Apalizar resultados de pruebas y ajustar el diseño

- Analizar resultados de pruebas y ajustar el diseño para optimizar funcionalidad y confiabilidad

- Documentar el flujo de diseño relacionado con LVS, ERC y extracción parásita como guía de referencia.

# **METODOLOGÍA**

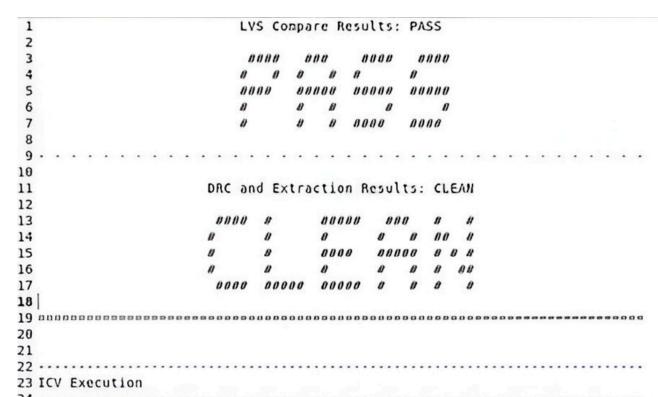

## RESULTADOS Verificación LVS

Resultado exitoso de la verificación LVS

Se realizaron pruebas de LVS en seis circuitos diferentes, logrando resultados exitosos en todos ellos, lo que confirmó la consistencia entre el diseño esquemático y el diseño físico de cada circuito.

#### Verificación ERC

Resultado exitoso de la verificación ERC

Además, se llevaron a cabo las pruebas de ERC en los mismos circuitos, obteniendo resultados exitosos que garantizaron el cumplimiento de las normativas eléctricas en el diseño.

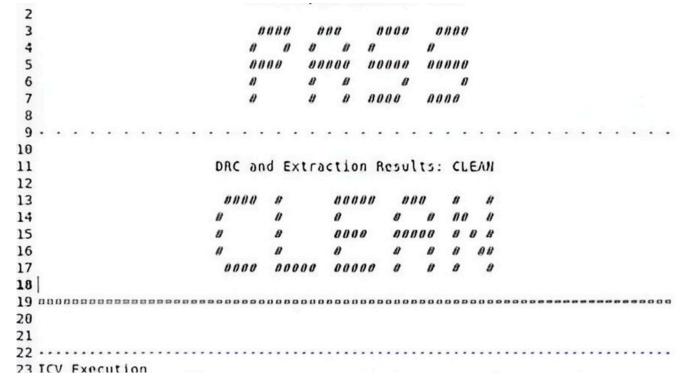

## Extracción parásita

. ENDS

.SUBCKT carry\_look\_ahead\_4bit a0a1 a2 a3b0 b1 b2b3 cin vsource s0 s1 s2 s3cout

\* \* Instance Section \*

- XI\_D4A6F1241n8 n9 s3I\_D4A6F1241:N\_5 N\_\_generated\_22 vsource XOR

XI\_D4A6F12410n8 n9 b3a3 cout I\_D4A6F12410:N\_7 I\_D4A6F12410:N\_8 vsource MORAND

XI\_D4A6F12411n12 n13 b1a1 n10 I\_D4A6F12411:N\_7 I\_D4A6F12411:N\_8 vsource MORAND

XI\_D4A6F12412b3 a3 n9I\_D4A6F12412:N\_5 I\_D4A6F12412:N\_6 vsource NOR

XI\_D4A6F12413b1 a1 n13I\_D4A6F12413:N\_5 I\_D4A6F12413:N\_6 vsource NOR

- XI D4A6F1242n11 n18 s2I D4A6F1242:N 5 N generated 23 vsource XOR XI D4A6F1243b2 a2 n11I D4A6F1243:N 5 I D4A6F1243:N 6 vsource XOR XI D4A6F1244n12 n13 s1I D4A6F1244:N 5 N generated 24 vsource XOR

- XI\_D4A6F124Scin n14 s0I\_D4A6F124S:N\_S N\_\_generated\_25 vsource XOR XI\_D4A6F1246b0 a0 n14I\_D4A6F1246:N\_S I\_D4A6F1246:N\_6 vsource XOR XI\_D4A6F1247b2 a2 n10n11 n8 I\_D4A6F1247:N\_7 I\_D4A6F1247:N\_8 vsource 22A0I XI\_D4A6F1248n14 cin a0b0 n12 I\_D4A6F1248:N\_7 I\_D4A6F1248:N\_8 vsource 22A0I

Se realizó la extracción de parásitos en tres circuitos, incluyendo el mapeo correspondiente; sin embargo, el deck generado solo fue simulable tras eliminar las resistencias y capacitancias parásitas, lo que limitó el análisis completo del diseño.

### **CONCLUSIONES**

- Se replicó el progreso previo del proyecto, estableciendo una base sólida para su desarrollo.

- Las pruebas de LVS confirmaron la consistencia entre el diseño esquemático y el diseño físico.

- Las pruebas de ERC permitieron detectar y corregir incumplimientos eléctricos.

- Se generó un deck más pequeño para facilitar el análisis en la extracción de parásitos, pero sin funcionar con los parásitos.

- Se implementaron modificaciones clave en los circuitos según los resultados de las pruebas, alineándolos con las especificaciones.

- Se elaboró una guía detallada sobre LVS, ERC y extracción de parásitos para futuros desarrolladores.

#### RECOMENDACIONES

- Revisar documentación previa, incluyendo manuales y guías, para sentar las bases del trabajo.

- Organizar archivos y carpetas de manera ordenada y consistente para facilitar su acceso.

- Actualizar el software del equipo para garantizar compatibilidad con herramientas y librerías.

- Desarrollar un script para automatizar la asignación de pines en los decks de extracción parásita.

- Desarrollar un script para automatizar el proceso de LVS, ERC y extracción parásita.

# **VÍDEO DEMOSTRATIVO**

### **BIBLIOGRAFÍA**

- "Etapa de verificación física de Diseño en Silicio vs. Esquemático (LVS) en el flujo de diseño para un chip a nanoescala", J. R. G. Rubio, Universidad del Valle de Guatemala, 2020.

- "Diseño de un circuito integrado con tecnología de 180 nm usando librerías de diseño de TSMC: uso avanzado de StarRC para la generación de un archivo HSPICE con componentes parásitos para su correcta simulación", C. A. L. Torres, Universidad del Valle de Guatemala, 2022.